FPG𝔸SIC

#FPGA #ASIC #VHDL #verilog #IP #Xilinx #Altera

PS: also might be intresting @ipcores

Community chat: https://t.me/hamster_kombat_chat_2

Website: https://hamster.network

Twitter: x.com/hamster_kombat

YouTube: https://www.youtube.com/@HamsterKombat_Official

Bot: https://t.me/hamster_kombat_bot

Last updated 11 months, 1 week ago

Your easy, fun crypto trading app for buying and trading any crypto on the market.

📱 App: @Blum

🤖 Trading Bot: @BlumCryptoTradingBot

🆘 Help: @BlumSupport

💬 Chat: @BlumCrypto_Chat

Last updated 1 year, 4 months ago

Turn your endless taps into a financial tool.

Join @tapswap_bot

Collaboration - @taping_Guru

Last updated 11 months, 4 weeks ago

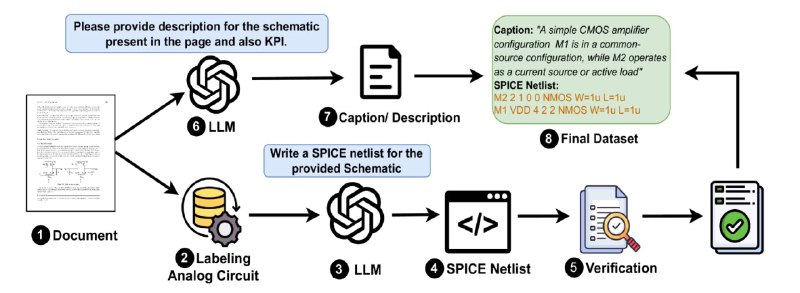

A Large-Scale SPICE Netlist Dataset for Analog Circuits by Harnessing AI

Masala-CHAI is the first fully automated framework leveraging large language models (LLMs) to generate Simulation Programs with Integrated Circuit Emphasis (SPICE) netlists.

Automating workflow could accelerate the creation of finetuned LLMs for analog circuit design and verification. We identify key challenges in this automation and evaluate the multi-modal capabilities of state-of-the-art LLMs, particularly GPT-4, to address these issues.

This approach aims to create an end-to-end SPICE netlist generator from circuit schematic images, tackling the long-standing hurdle of accurate netlist generation. Our framework demonstrates significant performance improvements, tested on approximately 2,100 schematics of varying complexity.

Links:

📄 https://arxiv.org/abs/2411.14299

*💾*** https://github.com/jitendra-bhandari/Masala-CHAI

DUTCTL: A Flexible Open-Source Framework for Rapid Bring-Up, Characterization, and Remote Operation of Custom-Silicon RISC-V SoCs

https://pulp-platform.org/docs/riscvmunich2024/RISCV_europe_summit_2024_DUTCTL_poster.pdf

CompressedLUT - a tool for lossless compression of lookup tables and generation of their hardware files in Verilog and C++ for RTL and HLS designs.

Links:? https://doi.org/10.1145/3626202.3637575

*?*** https://github.com/kiabuzz/CompressedLUT

#acceleration #LUT #lookuptable #lossless #compression #table-size-reduction #table-based-function-implementation

@fpgasic

Community chat: https://t.me/hamster_kombat_chat_2

Website: https://hamster.network

Twitter: x.com/hamster_kombat

YouTube: https://www.youtube.com/@HamsterKombat_Official

Bot: https://t.me/hamster_kombat_bot

Last updated 11 months, 1 week ago

Your easy, fun crypto trading app for buying and trading any crypto on the market.

📱 App: @Blum

🤖 Trading Bot: @BlumCryptoTradingBot

🆘 Help: @BlumSupport

💬 Chat: @BlumCrypto_Chat

Last updated 1 year, 4 months ago

Turn your endless taps into a financial tool.

Join @tapswap_bot

Collaboration - @taping_Guru

Last updated 11 months, 4 weeks ago